## The SystemC OCP Models

An Overview of the SystemC Models for the Open Core Protocol

Alan Kamas

NASCUG 9/29/2004

© Alan Kamas 2004 www.kamas.com

-1

This talk will give you an overview of the OCP (Open Core Protocol) connection and the set of SystemC models built to simulate it.

This talk is copyright 2004 by Alan Kamas. The open core protocol specification mentioned in this talk is the intellectual property of OCP IP: see www.ocpip.org for more information.

| □ Anssi Hav            | verinen, Nokia         |  |

|------------------------|------------------------|--|

| □ Norman \             | Weyrich, Synopsys Inc. |  |

| □ Yann Baj<br>Prosilog | ot and Stéphane Guntz, |  |

| □ Joe Chou             | , Sonics Inc.          |  |

| □ James Al             | dis, Texas Instruments |  |

| OCP-IP &               | the OCP SLD-WG         |  |

The OCP Models are the work of many people.

My work on the project was paid for by Sonics, Inc. Sonics, as with the other companies here, has donated its SystemC work to the project.

In addition to providing code and design, Anssi Haverinen is chair of the OCP System Level Design Working Group which is responsible for the channel models.

Norman Weyrich (formerly of Synopsys Inc.) was one of the original developers and worked on the generic model.

Yann Bajot and Stephane Guntz have built layer adaptors and contributed to the TL2 models.

Joe Chou of Sonics has contributed to design and code of the OCP models.

James Aldis has contributed work on the channel monitor.

There are many more members of the OCP SLD-WG from many other companies that have contributed to the project.

| Outline          |                                    |   |

|------------------|------------------------------------|---|

| □ What is th     | e OCP Channel?                     |   |

| OCP Hardy        | ware view                          |   |

| □ OCP Syste      | mC Channel Models                  |   |

| ■ Generic        |                                    |   |

| OCP TL1          |                                    |   |

| OCP TL2          |                                    |   |

| Layer Ada        | •                                  |   |

| Availability     | /                                  |   |

| ☐ Future Dir     | ections                            |   |

| NASCUG 9/29/2004 | © Alan Kamas 2004<br>www.kamas.com | 3 |

First we'll cover a brief introduction to OCP channel and how it works at the hardware level. Then we'll look at the SystemC models for the OCP channel covering some of the decisions that went into their design. Finally, we'll take at peek at where the work is headed in the future.

The OCP (Open Core Protocol) is an open standard for connecting the blocks of a system on chip. The Open Core Protocol is point to point – connecting one block to another – and is not a bus specification (connecting many blocks to many blocks). The standard was developed to be configurable and flexible to work with many different types of IP.

| $\cap \cap$ to $\cap$ .                                                  | ᇈ   | lic Memb                                   | ~ L      | 1:0+                             |

|--------------------------------------------------------------------------|-----|--------------------------------------------|----------|----------------------------------|

| しんとート とし                                                                 | Ш   | )II(;  Y  <b>(</b> E    )                  | er       | 1151                             |

| <u> </u>                                                                 |     |                                            | <u> </u> |                                  |

|                                                                          |     |                                            |          |                                  |

|                                                                          |     |                                            |          |                                  |

| 3rdeye Technology                                                        |     | GDA Technologies                           |          |                                  |

| Accent                                                                   |     | GeoLogic<br>HDL Design House               |          | Siroyan<br>Sonics                |

| Acculent Corporation                                                     |     | HUL Design House<br>Hughes Network Systems |          | SpiraTech                        |

| Advanced Architectures                                                   |     | Icera Semiconductor                        |          | STARC                            |

| □ Alcatel                                                                |     | IDT                                        |          | STMicroelectronics               |

| ☐ Amphion<br>☐ ARC International                                         |     | Infineon                                   |          | Summit Design                    |

|                                                                          | - 5 |                                            |          | Synergetic Computing Systems     |

| Artisan Components                                                       |     | Kawasaki                                   |          | Synopsys                         |

| <ul> <li>□ ATI Technologies</li> <li>□ AXYS Design Automation</li> </ul> |     | LIRMM                                      |          | Tampere University of Technology |

| Beach Solutions                                                          |     | LSI Logic                                  |          | Technical University of Denmark  |

| Bitbovs                                                                  |     | LTRIM Technologies                         |          | TechOnLine                       |

| □ Broadcom                                                               |     | Manhattan Routing, Inc.                    |          | Tensilica                        |

| Cadence Design Systems                                                   |     | Mentor Graphics                            |          | Texas Instruments                |

| CAST, Inc.                                                               |     | Micronas                                   |          | TNI-Valiosys                     |

| Chip Implementation Center                                               |     | MIPS Technologies                          |          | Toshiba Semiconductor Group      |

| Control Net India                                                        |     | National Tsing Hua University              |          | Tower Semiconductor              |

| Coware                                                                   |     | NEC                                        |          | TranSwitch                       |

| DAFCA                                                                    |     | NoBug                                      |          | TSMC<br>UFCG                     |

| □ Denali                                                                 |     | Nokia<br>Paradigm Works                    |          | UMC                              |

| Design And Reuse                                                         | H   |                                            |          | University of British Columbia   |

| Dolphin Integration                                                      |     | PUCRS                                      |          | UC Berkelev                      |

| Duolog Duolog                                                            | ä   |                                            |          | Verisity                         |

| □ eASIC                                                                  | - 5 |                                            | - 5      |                                  |

| □ ECSI                                                                   |     |                                            |          | Virtual IP Group                 |

| □ EDA Cafe                                                               |     | Royal Institute of Technology              |          | Virtual Silicon                  |

| □ eInfochips                                                             |     | Si 2                                       |          | VSIA                             |

| ☐ Esterel Technologies                                                   |     | Siemens                                    |          | White Eagle Systems Technology   |

| ☐ First Silicon Solutions                                                |     | Silicon Interfaces                         |          | WiQuest Communications           |

| ☐ Flextronics Semiconductor                                              |     |                                            |          | Yamaha Corporation               |

|                                                                          |     | Silicon & Software Systems                 |          | YogiTech                         |

| NASCUC 9/29/2004                                                         |     | © Alan Kamas 2004                          |          |                                  |

| NASCUG 9/29/2004                                                         |     | © Alan Kamas 2004<br>www.kamas.com         |          |                                  |

Many companies and universities are involved with the Open Core Protocol

| 0001                  |                                    |          |

|-----------------------|------------------------------------|----------|

| OCP Laye              | ring & Terminolog                  | <u> </u> |

| □ Signals             |                                    |          |

| ■ Wires &             | fields                             |          |

| □ Phases              |                                    |          |

| Request,              | Data handshake, Respor             | ıse      |

| □ Transfers           |                                    |          |

| A Read of             | or Write                           |          |

| □ Transaction         | n                                  |          |

| A comple<br>transfers | ete burst of one or more           |          |

| NASCUG 9/29/2004      | © Alan Kamas 2004<br>www.kamas.com | 6        |

A quick overview of OCP terminology.

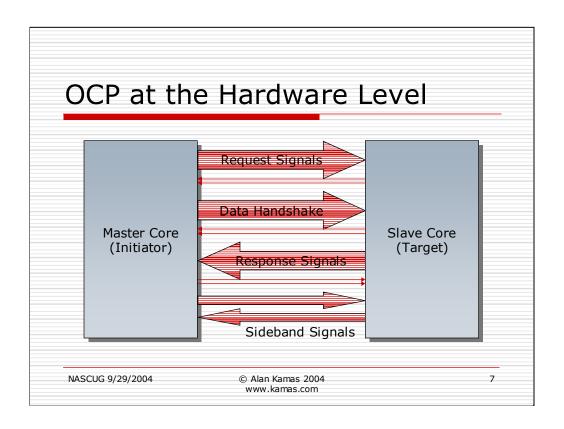

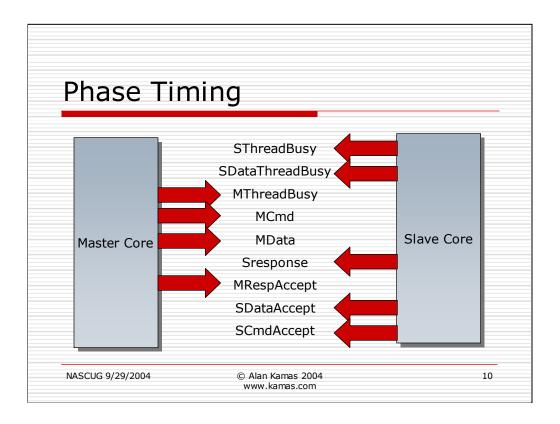

So, what does this OCP connection look like? At the hardware level, the Open Core Protocol is a collection of signals between the two cores. There is a handshake path for requests, another (optional) handshake path for request data, and a separate path for responses (which includes the response data). Note that there are also a set of sideband signals between the cores. These signals include interrupt, flags, and error signaling.

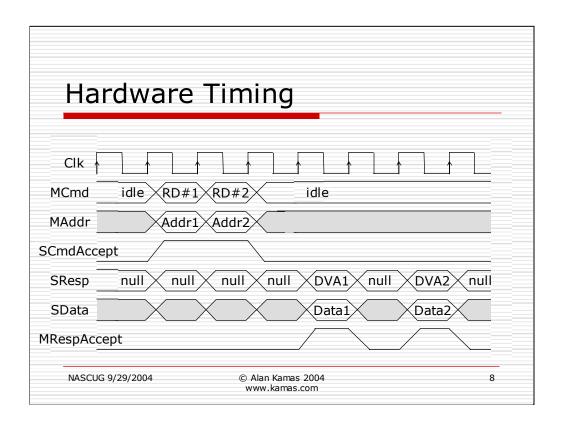

One interesting aspect of the OCP connection is that it allows responses to be pipelined. That is, it is possible to send a number of requests before receiving any responses. Here, read request #1 is sent, and then read request #2 is sent and then the response #1 is sent and then response #2. The responses may be sent anytime after the request has been received. Conceivably, this could be a long time after. The only restriction is that responses are returned in the same order as the requests.

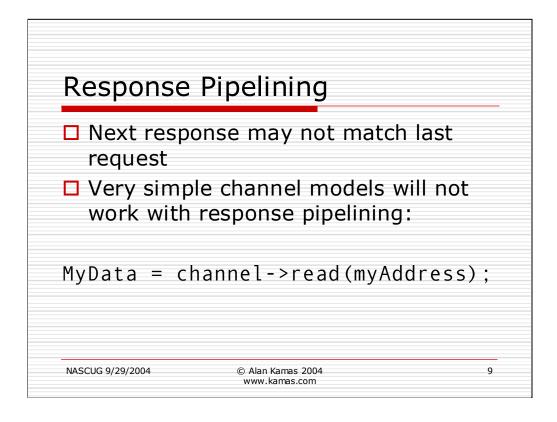

Jumping ahead here, one aspect of pipelined responses is that it limits the type of SystemC model you can have. Blocking calls like this one: myData = read( myAddress );

Don't always work since the response data you are getting could be from a previous command. You could model the OCP without the separate request and response paths but then you would be missing some of the flexibility and throughput of the OCP connection.

Back to the hardware model.

In addition to response pipelining, communications over the OCP connection must follow a certain order. Here the busy signals must be sent before the request. The data must start after the request, and the response comes after that. A cycle accurate model of the OCP connection must follow the same ordering.

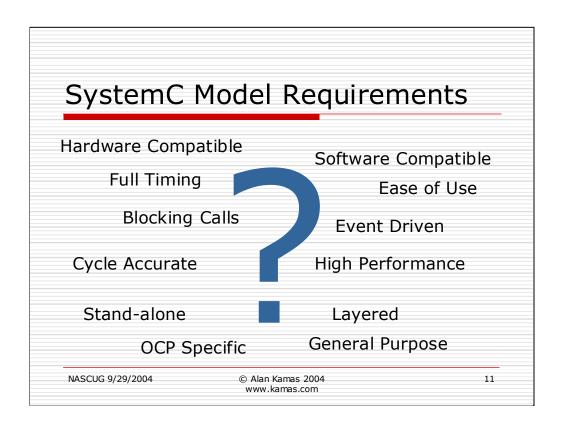

Now that we know a little bit about how the Open Core Protocol works in the hardware, we're ready to consider the SystemC models. The question then becomes, what sort of SystemC model is needed? Is the model for hardware interfacing or architecture exploration? Should it be cycle accurate or should it run at a more abstract level? Should the phases of a transfer be observed or is model performance the priority? Should the model be stand-alone or layered?

| ☐ Generic I | Model        |  |

|-------------|--------------|--|

|             | tion Level 1 |  |

|             | tion Level 2 |  |

| OCP TL1     |              |  |

| OCP TL2     |              |  |

| □ Layer Ad  | aptors       |  |

The answer is YES! To meet different modeling needs, there are OCP channel models at different abstraction levels layered upon a generic transaction level channel. The OCP channel models include a generic transaction level channel model for sending requests and responses of a templated data type back and forth. Built on top of this are the OCP specific channels. The OCP Transaction Level 1 model is a low level, cycle-accurate model with all of the phases and timing of the hardware. The OCP Transaction Level 2 model runs at a higher level of abstraction by combining the request and data phase and allowing whole bursts to be sent as single TL2 commands.

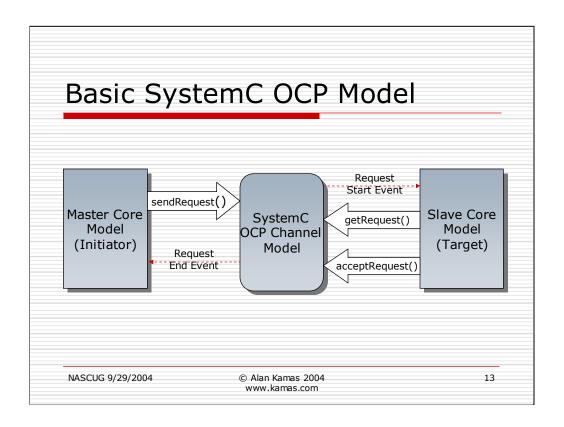

All of the models have a request path through the channel. The master calls a function (sendRequest) in the channel model through a port that is connected to the channel. The channel takes the request and triggers an event (RequestStartEvent) that the Slave is sensitive to. This may wake up a SystemC process in the slave which then calls the getRequest function in the channel. At a possibly later time, the Slave may call the channel's acceptRequest() function to accept the request. The channel then triggers the RequestEndEvent event. The Master is sensitive to this event as it lets the Master know that old request is finished and a new request may now begin.

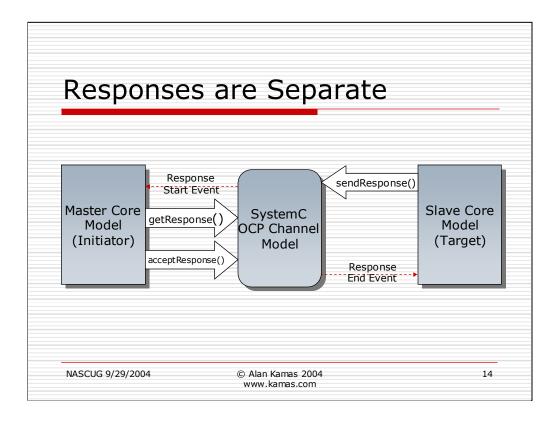

A separate path for responses allows for response pipelining.

| □ Based on<br>Transaction | hannel Model initial work of Gener on Level Channel. Data type and format |    |

|---------------------------|---------------------------------------------------------------------------|----|

| NASCUG 9/29/2004          | © Alan Kamas 2004<br>www.kamas.com                                        | 15 |

Useful for experimentation with channel modeling. Hooks to build connections with EDA tools Underlying layer for TL1 and original TL2

# Generic Channel Code // Master Core Model Example. // Send a read command over generic channel // Channel uses TDataCl as its data class TDataCl \*cDataPtr; cDataPtr = MasterPort->GetDataCl(); cDataPtr->MputMAddr(Addr); MasterPort->MputReadRequest();

An example of a request being sent over the generic channel. The generic channel is instantiated with a TDataCl class type template. Thus the generic channel can carry any type of data, address, etc. Here, the values for the next request are loaded into the channel and then the "MputReadRequest" command is called to start the new request and to toggle the previously loaded data values unto the channel.

| Transaction Level 1 TL1 OCP Channel                                |    |

|--------------------------------------------------------------------|----|

| ☐ Cycle Accurate☐ Follows phase ordering of the                    |    |

| OCP transfer cycle                                                 |    |

| <ul><li>□ Clock Driven</li><li>□ Uses all OCP parameters</li></ul> |    |

| □ Request / Update                                                 |    |

| ☐ All OCP signals supported                                        |    |

| OCP signal monitor available                                       |    |

| NASCUG 9/29/2004 © Alan Kamas 2004<br>www.kamas.com                | 17 |

## The Transaction Level One

This OCP SystemC model attempts to fully capture the timing and ordering of the hardware OCP connection. It is built on top of the generic channel with a data class for full OCP support and OCP specific commands for ease of use.

## OCP TL1 Code // Send a write request over the OCP TL1 // Channel (using blocking commands) OCPRequestGrp<Td, Ta> req; req. MCmd = OCP\_MCMD\_WR; req. MAddr = 0x0401; MasterPort->startOCPRequestBlocking(req); OCPDataHSGrp<Td> datahs; datahs. MData = myData; MasterPort->startOCPDataHSBlocking(datahs); NASCUG 9/29/2004 © Alan Karmas 2004 www.karmas.com

Here is a sequence of commands to send a write request over the OCP TL1 channel. Note that here the channel uses an OCP specific data structure to hold the request. This structure supports all of the OCP request signals including MCmd (command type), and MAddr (the address). The OCP TL1 channel model also has an independent data path. Here, the write data is sent after the write command.

# OCP TL1 Code — non blocking // Send a read request over the OCP TL1 Channel (using non-blocking commands) OCPRequestGrp<Td> req; req.MCmd = OCP\_MCMD\_RD; req.MThreadID = 1; req.MAddr = 0x0401; if (MasterPort->sendOCPRequest(req)) { cout << "Request Sent" << endl; } NASCUG 9/29/2004 © Alan Kamas 2004 www.kamas.com

The OCP TL1 interface supports both blocking and non-blocking calls.

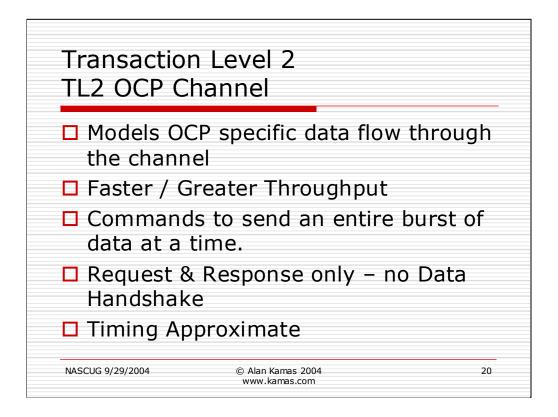

The OCP Transaction Level 2 channel is designed to work at a higher abstraction level. The phase structure is simplified, consolidating the data handshake phase into the request group. The request and response groups are expanded so that an entire burst of OCP transfers may be sent with a single command. The TL2 channel has better performance and greater throughput but the downside is that the timing will not be cycle accurate as it is in TL1.

##

Here a burst write request of 4 data words is sent over the OCP TL2 channel. The whole burst is sent as a single command. Note that, as with the OCP TL1 channel, both blocking and non-blocking calls are available.

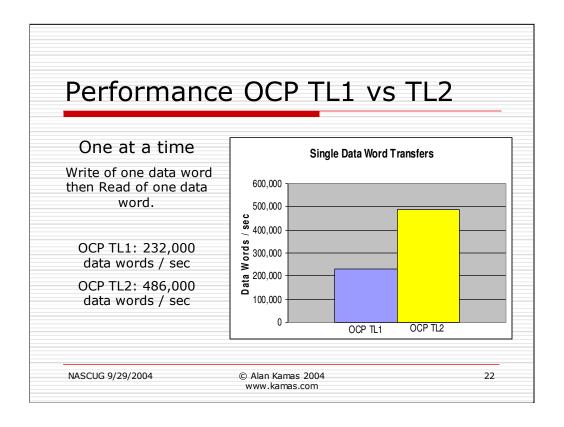

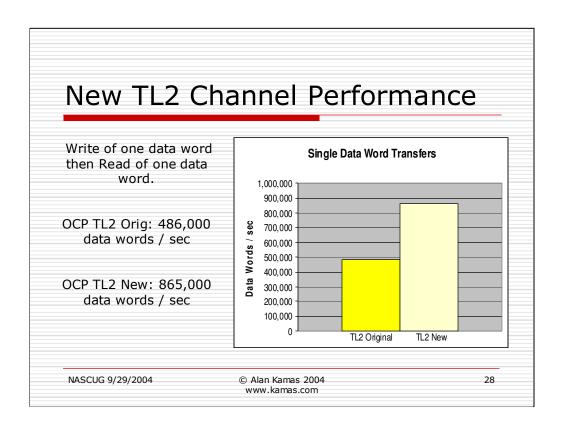

In this benchmark test the master sends a write command and then a read command. This sequence is looped 10 million times.

As you can see from the chart, the TL2 channel has about twice the throughput of the TL1 channel.

For TL1: data handshake is used for the writes, which slows it down. Also, the TL1 master uses one SystemC thread method (to handle requests) while the TL2 models are completely event driven.

## Here are the test details:

In each of these tests, a simple master is connected to a simple core through the OCP channel model. The OCP Channel has data handshake with command, data, and response accept. For writes, the command goes first and then the data goes in the next cycle.

These tests were run on a dual processor Pentium III 1.26GHz machine. All simulations ran on a single processor. The tests were compiled under Linux with gcc 2.96 using the "-O" flag and the standard OSCI SystemC library. The first test is a single data word write command followed by a single data word read.

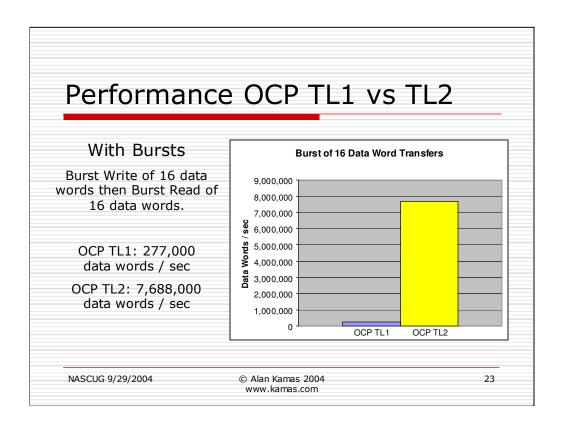

The real speed up from the TL2 channel is how it handles bursts. Here the master sends a burst 16 write command followed by a burst 16 read command, and the sequence is repeated.

The OCP TL1 channel sends each command of the burst individually. A burst 16 read is 16 read commands and 16 responses. The OCP TL2 channel allows the cores to send the whole burst as one command.

## Here are the test details:

In each of these tests, a simple master is connected to a simple core through the OCP channel model. The OCP Channel has data handshake with command, data, and response accept. For writes, the command goes first and then the data goes in the next cycle.

These tests were run on a dual processor Pentium III 1.26GHz machine. All simulations ran on a single processor. The tests were compiled under Linux with gcc 2.96 using the "-O" flag and the standard OSCI SystemC library. This second test is a burst 16 data word write command followed by a burst 16 data word read.

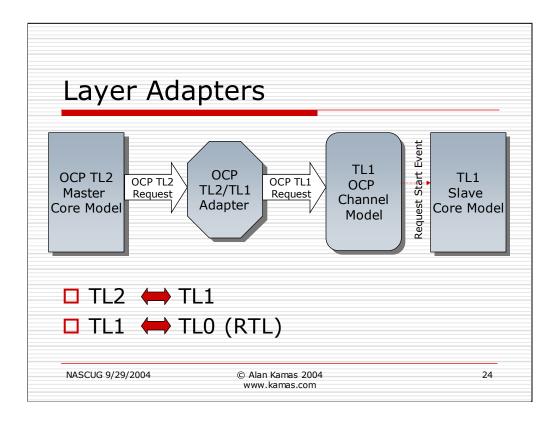

One problem with multiple channel model types is getting cores written for different models to work together.

The layer adapters convert the interface from one OCP layer to another. Here a Core model has been written to work with the OCP TL2 channel. The layer adapter allows it to work with an OCP TL1 channel.

The layer adapters may even be chained together allowing an OCP TL2 core to communicate with an RTL (TL0) channel.

| Gettina the      | e OCP Channel Model                | S    |

|------------------|------------------------------------|------|

|                  |                                    |      |

| ■ Available 1    | for download from OCP-             | -IP: |

| http://ww        | w.ocpip.org/socket/syst            | temc |

| □ Click on th    |                                    |      |

| ☐ Fill in the    | form                               |      |

| □ Read the       |                                    |      |

|                  |                                    |      |

| L Download       | the Channel Models                 |      |

|                  |                                    |      |

|                  |                                    |      |

| NASCUG 9/29/2004 | © Alan Kamas 2004<br>www.kamas.com | 25   |

| Future Dir             | rections                           |    |

|------------------------|------------------------------------|----|

| □ Performar □ OSCI TLM | nce OCP TL2 Channel                |    |

| NASCUG 9/29/2004       | © Alan Kamas 2004<br>www.kamas.com | 26 |

A quick look into the future for the OCP channel models

| New OCP          | TL2 Channel                        |    |

|------------------|------------------------------------|----|

| ☐ Available      | this Fall                          |    |

| ☐ Timing Va      | lues for greater accuracy          |    |

| Higher Th        | roughput                           |    |

| □ Written fo     | or Performance                     |    |

| No layer         | ing                                |    |

| ■ No reque       | est / update                       |    |

| Loss of g        | generic commands                   |    |

|                  |                                    |    |

| NASCUG 9/29/2004 | © Alan Kamas 2004<br>www.kamas.com | 27 |

There will be a new performance version of the OCP TL2 available this Fall. The new TL2 channel adds timing points that are passed through the channel so that approximately cycle accurate timing may be achieved at the TL2 level. The new OCP TL2 channel was rewritten with performance as the goal and runs faster, however because it is not layered, it does not support all of generic level commands.

The new TL2 channel has about 75% more throughput then the original channel. This is true for burst transfers as well.

The Open SystemC Initiative is also working on developing transaction level models in SystemC.

| Further In                                | formation                          |    |

|-------------------------------------------|------------------------------------|----|

| www.ocpip  OCP Specification  White paper | fication                           | e: |

| ■ Documen<br>■ Source co                  |                                    |    |

| ■ Example                                 | · · ·                              |    |

| NASCUG 9/29/2004                          | © Alan Kamas 2004<br>www.kamas.com | 30 |

There is more information available online.